計算機網絡基礎(第2版)——計算機軟件及網絡應用技術開發培訓指南

《計算機網絡基礎(第2版)》作為計算機應用與軟件技術專業的核心培訓教材,全面系統地介紹了計算機網絡的基本原理、關鍵技術及其在現代軟件開發與網絡應用中的實踐方法。本書旨在幫助讀者構建堅實的網絡知識體系,掌握計算機軟件及網絡應用技術的開發技能。

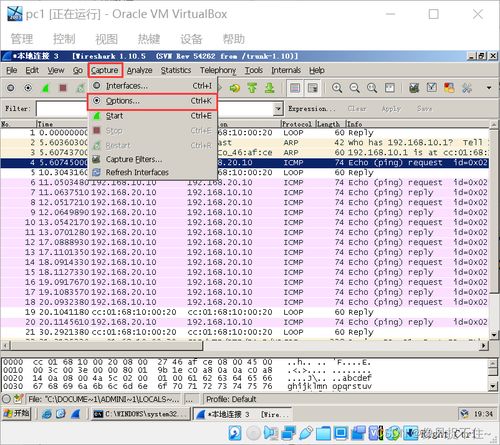

在內容編排上,本書首先從計算機網絡的基本概念入手,詳細解析了OSI與TCP/IP參考模型、數據通信原理、局域網與廣域網技術等基礎知識。隨后,深入探討了網絡協議(如HTTP、FTP、SMTP)、網絡設備(如路由器、交換機)以及網絡安全機制,為軟件開發者提供了必要的網絡環境理解。

針對計算機軟件及網絡應用技術的開發,本書專門設置了實踐章節,涵蓋網絡編程基礎、Socket通信、Web服務開發(包括RESTful API設計)、云計算與物聯網應用等熱點領域。通過豐富的案例分析和實驗指導,讀者可以學習如何利用網絡技術構建分布式系統、優化軟件性能,并應對實際開發中的網絡問題。

第2版更新了最新技術趨勢,如5G網絡、軟件定義網絡(SDN)和容器化部署(Docker與Kubernetes),確保內容與行業需求同步。本書不僅適用于高校教學,還可作為IT從業者提升網絡開發能力的自學參考書,幫助讀者在快速發展的信息技術領域中保持競爭優勢。

如若轉載,請注明出處:http://m.digitalshape.cn/product/33.html

更新時間:2026-04-13 05:19:18